Quelle: Freepik

Im DFG-geförderten Projekt „Heuristics for Heterogeneous Memory“ (H2M) entwickeln die RWTH Aachen University und der französische Projektpartner Inria gemeinsam eine Unterstützung neuer Speichertechnologien wie z.B. High Bandwidth Memory (HBM) und Non Volatile Memory (NVM). Diese Technologien kommen neben dem üblichen Dynamic Random Access Memory (DRAM) immer häufiger in HPC-Systemen als zusätzliche Speicher zum Einsatz. HBM bietet eine höhere Bandbreite als klassischer DRAM, ist dafür aber auch wesentlich kleiner. NVM stellt größere Kapazitäten zur Verfügung, ist jedoch langsamer im Vergleich zum DRAM. Durch die unterschiedlichen Charakteristiken und Kapazitätsgrenzen stellt sich somit die Frage, wie Systeme mit heterogenem Speicher effizient eingesetzt werden können und in welchem Speicher Daten abgelegt werden sollen.

Christian Terboven, Brice Goglin, Emmanuel Jeannot, Clément Foyer, Anara Kozhokanova und Jannis Klinkenberg

Quelle: Eigene Darstellung

Zur Verwendung der neuen Speichertechnologien müssen Anwendungen aktuell noch stark modifiziert werden und plattform- oder herstellerspezifische Application Programming Interfaces (APIs) eingesetzt werden.

Seit Beginn des Projektes 2021 verfolgt H2M das Ziel, portable Schnittstellen bereitzustellen, um verfügbare Speicher sowie deren Eigenschaften zu identifizieren und den Zugriff zu ermöglichen. Darauf basierend sollen Allokationsabstraktionen und Heuristiken entwickelt werden, um Anwendungsentwickler*innen sowie Laufzeitsystemen eine Kontrolle zu geben, in welchem Speicher Daten abgelegt und wann Daten zwischen unterschiedlichen Arten von Speichern verschoben werden sollen. In unserem Blogbeitrag 2021 haben wir den Beginn des Projektes bereits vorgestellt. Zu diesem Zeitpunkt war noch unklar, wie Abstraktionen und Heuristiken aussehen sollen. Nun sind die Forschenden schon einen großen Schritt weiter und haben Allokationsfunktionen entwickelt.

Mit den richtigen Traits zum richtigen Speicher

Die Idee dabei ist, die sonst üblichen Memory Allokationsfunktionen wie malloc (in C) und new (in C++) durch eine neue Allokationsfunktion (h2m_alloc_w_traits) zu abstrahieren. Mit dieser können Anwendungsentwickler*innen einer Allokation zusätzliche Eigenschaften (sogenannte Traits) übergeben, die z.B. beschreiben, wie die Daten im Verlauf der Applikation verwendet werden bzw. wie auf die Daten zugegriffen wird oder welche Voraussetzungen die Allokation erfüllen muss. Dies ist in folgendem Beispiel zu sehen.

int err;

double* data_item;

size t N = 1000 * sizeof(double); // desired size (in bytes)

// Specify allocation traits (requirements and hints)

h2m_alloc_trait_t traits[5] = {

h2m_atk_access_mode, h2m_atv_access_mode_readwrite,

h2m_atk_access_origin, h2m_atv_access_origin_multiple_threads,

h2m_atk_access_pattern, h2m_atv_access_pattern_strided,

h2m_atk_access_stride, 3 /* in bytes */,

h2m_atk_access_freq, 2000, /* e.g., accesses per sec */};

// Finally allocate memory

data_item = (double*) h2m_alloc_w_traits(N, &err, 5, traits);

In diesem Code-Beispiel wird für die Allokation angegeben, dass auf die Daten von mehreren Threads in lesender und schreibender Form zugegriffen wird und das voraussichtlich nicht linear, sondern mit einem Stride von 3. Das bedeudet, dass nur jeder 3. Wert verwendet wird. Threads sind eigenständige Ausführungsstränge, die gleichzeitig bearbeitet werden können, und kommen oft bei paralleler Programmierung zum Einsatz, um Applikationen zu beschleunigen.

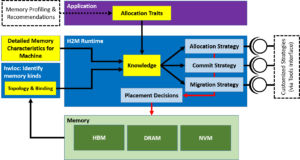

Wie Abbildung 1 zeigt, kann das H2M Laufzeitsystem dann mit Hilfe von Strategien den geeigneten Speicher zur Ablage der Daten bestimmen. Dabei werden sowohl Traits als auch die im System verfügbaren Speichertechnologien berücksichtigt. H2M stellt unter anderem simple Basis-Strategien zur Verfügung, bietet aber auch die Möglichkeit, über ein Interface benutzerdefinierte Strategien zu erstellen und zu verwenden.

Abbildung 1: Übersicht der H2M Komponenten und des Zusammenspiels mit Applikation und der Systemumgebung Quelle: Eigene Darstellung

Breit aufgestellt – Evaluation auf mehreren Architekturen und aktuelle Forschungsrichtung

Das neue Konzept wird mit diversen Proxy Applikationen, sogenannten Mini-Apps, und Benchmarks auf unterschiedlichen Architekturen evaluiert. Beispiele dafür sind Intel‘s KNL Architektur, die neben DRAM auch mit MCDRAM (HBM) Speichermodulen ausgestattet ist. Dieser ist zwar kleiner, bietet dafür aber eine höhere Bandbreite. Darüber hinaus wurde eine Architektur evaluiert, die neben üblichem DDR4 große Mengen an Intel Optane DC Persistent Memory (NVM oder non-volatile Memory) besitzt., Dieser ist zwar langsamer, stellt im Gegenzug allerdings mehr Kapazität bereit.

Bisher lag der Fokus der Forschung auf Szenarien, bei denen Datenobjekte einmalig in bestimmten Speichertypen abgelegt wurden und für den Rest der Programmausführung dort bleiben. Aktuell und in Zukunft wird jedoch auch evaluiert, inwiefern eine dynamische Verschiebung von Daten zwischen Speichertypen zur Laufzeit Effizienzsteigerungen erzielen kann. Das ist z.B. dann interessant, wenn Applikationen aus mehreren Ausführungsphasen bestehen, in denen die Daten unterschiedlich verwendet werden oder in denen sich Zugriffsmuster auf Daten gravierend ändern.

Verantwortlich für die Inhalte dieses Beitrags sind Jannis Klinkenberg und Janin Vreydal.